# OpenSPARC T2<sup>TM</sup> Supplement to the *UltraSPARC Architecture* 2007

Draft D1.4.2, 01 Aug 2007

Privilege Levels:

Hyperprivileged, Privileged, and Nonprivileged

Distribution: Public

Sun Microsystems, Inc. 4150 Network Circle Santa Clara, CA 95054 U.S.A. 650-960-1300

Part No: 950-5556-01 Revision: Draft 1.4, 01 Aug 2007 Copyright 2002–2006 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 USA. All rights reserved.

This product or document is protected by copyright and distributed under licenses restricting its use, copying, distribution, and decompilation. No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors, if any. Third-party software, including font technology, is copyrighted and licensed from Sun suppliers.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and other countries, exclusively licensed through X/Open Company, Ltd. For Netscape Communicator<sup>™</sup>, the following notice applies: Copyright 1995 Netscape Communications Corporation. All rights reserved.

Sun, Sun Microsystems, the Sun logo, Solaris, and VIS are trademarks, registered trademarks, or service marks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The OPEN LOOK and Sun<sup>TM</sup> Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

**RESTRICTED RIGHTS**: Use, duplication, or disclosure by the U.S. Government is subject to restrictions of FAR 52.227-14(g)(2)(6/87) and FAR 52.227-19(6/87), or DFAR 252.227-7015(b)(6/95) and DFAR 227.7202-3(a).

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2002–2006 Sun Microsystems, Inc., 4150 Network Circle • Santa Clara, CA 950540 Etats-Unis. Tous droits réservés.

Des parties de ce document est protégé par un copyright© 1994 SPARC International, Inc.

Ce produit ou document est protégé par un copyright et distribué avec des licences qui en restreignent l'utilisation, la copie, la distribution, et la décompilation. Aucune partie de ce produit ou document ne peut être reproduite sous aucune forme, par quelque moyen que ce soit, sans l'autorisation préalable et écrite de Sun et de ses bailleurs de licence, s'il y en a. Le logiciel détenu par des tiers, et qui comprend la technologie relative aux polices de caractères, est protégé par un copyright et licencié par des fournisseurs de Sun.

Sun, Sun Microsystems, le logo de Sun, Solaris, et VIS sont des marques de fabrique ou des marques déposées, ou marques de service, de Sun Microsystems, Inc. aux Etats-Unis et dans d'autres pays. Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

L'interface d'utilisation graphique OPEN LOOK et Sun™ a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une licence non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciés de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui en outre se conforment aux licences écrites de Sun.

CETTE PUBLICATION EST FOURNIE "EN L'ETAT" ET AUCUNE GARANTIE, EXPRESSE OU IMPLICITE, N'EST ACCORDEE, Y COMPRIS DES GARANTIES CONCERNANT LA VALEUR MARCHANDE, L'APTITUDE DE LA PUBLICATION A REPONDRE A UNE UTILISATION PARTICULIERE, OU LE FAIT QU'ELLE NE SOIT PAS CONTREFAISANTE DE PRODUIT DE TIERS. CE DENI DE GARANTIE NE S'APPLIQUERAIT PAS, DANS LA MESURE OU IL SERAIT TENU JURIDIQUEMENT NUL ET NON AVENU.

# Contents

| 1 | Ope  | OpenSPARC T2 Basics   |                                                  |  |  |

|---|------|-----------------------|--------------------------------------------------|--|--|

|   | 1.1  | Background            |                                                  |  |  |

|   | 1.2  | OpenSPARC T2 Overview |                                                  |  |  |

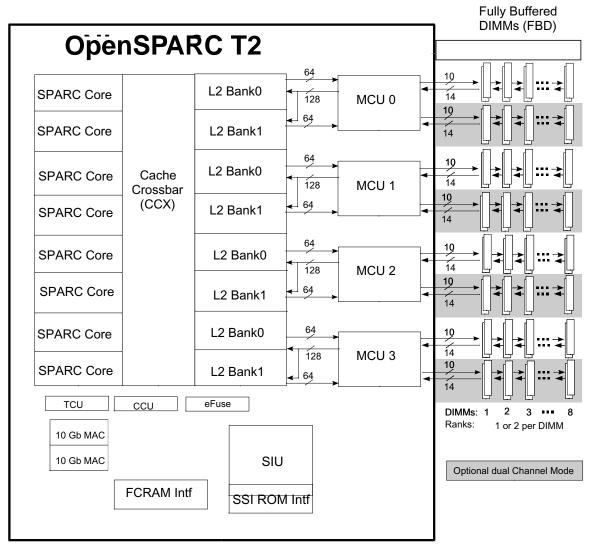

|   | 1.3  | 1                     | ARC T2 Components5                               |  |  |

|   |      | 1.3.1                 | SPARC Physical Core                              |  |  |

|   |      | 1.3.2                 | L2 Cache                                         |  |  |

|   |      | 1.3.3                 | Memory Controller Unit (MCU) 5                   |  |  |

|   |      | 1.3.4                 | Noncacheable Unit (NCU)                          |  |  |

|   |      | 1.3.5                 | System Interface Unit (SIU) 6                    |  |  |

|   |      | 1.3.6                 | SSI ROM Interface (SSI)                          |  |  |

| 2 | Data | a Formats             |                                                  |  |  |

| 3 | Reg  | isters                | 9                                                |  |  |

|   | 3.1  | Ancillar              | y State Registers (ASRs)9                        |  |  |

|   |      | 3.1.1                 | Tick Register (TICK) 10                          |  |  |

|   |      | 3.1.2                 | Program Counter (PC) 11                          |  |  |

|   |      | 3.1.3                 | Floating-Point State Register (FSR) 11           |  |  |

|   |      | 3.1.4                 | General Status Register (GSR) 11                 |  |  |

|   |      | 3.1.5                 | Software Interrupt Register (SOFTINT) 12         |  |  |

|   |      | 3.1.6                 | Tick Compare Register (TICK_CMPR) 12             |  |  |

|   |      | 3.1.7                 | System Tick Register (STICK) 13                  |  |  |

|   |      | 3.1.8                 | System Tick Compare Register (STICK_CMPR) 13     |  |  |

|   | 3.2  | Privileg              | ed PR State Registers14                          |  |  |

|   |      | 3.2.1                 | Trap State Register (TSTATE)    14               |  |  |

|   |      | 3.2.2                 | Processor State Register (PSTATE) 15             |  |  |

|   |      | 3.2.3                 | Trap Level Register (TL) 16                      |  |  |

|   |      | 3.2.4                 | Current Window Pointer (CWP) Register 17         |  |  |

|   |      | 3.2.5                 | Global Level Register (GL) 17                    |  |  |

|   | 3.3  | Hyperp                | rivileged Registers                              |  |  |

|   |      | 3.3.1                 | Hypervisor Processor State Register (HPSTATE) 18 |  |  |

|   |      | 3.3.2                 | Hypervisor Trap State Register (HTSTATE) 18      |  |  |

|   |      | 3.3.3                 | Hypervisor Interrupt Pending Register (HINTP) 19 |  |  |

|   |      | 3.3.4<br>3.3.5<br>3.3.6 | Hypervisor Trap Base Address Register (HTBA)    |

|---|------|-------------------------|-------------------------------------------------|

|   |      | 3.3.7                   | Halt                                            |

| 4 | Inst | ruction Fo              | rmat                                            |

| 5 | Inst |                         | efinitions                                      |

|   | 5.1  |                         | on Set Summary                                  |

|   | 5.2  |                         | ARC T2-Specific Instructions                    |

|   | 5.3  | 5.3.1                   | ad and Store Instructions                       |

| 6 | Trap | os                      |                                                 |

|   | 6.1  | Trap Lev                | els                                             |

|   | 6.2  | Trap Beh                | avior                                           |

|   | 6.3  | Trap Ma                 | sking                                           |

| 7 | Inte | -                       | dling                                           |

|   | 7.1  | Interrup                | t Flow                                          |

|   |      | 7.1.1                   | Sources                                         |

|   |      | 7.1.2                   | Dispatching                                     |

|   |      | 7.1.3                   | States                                          |

|   |      | 7.1.4<br>7.1.5          | Prioritizing                                    |

|   |      | 7.1.5                   | Servicing                                       |

|   | 7.2  |                         | errupt Registers                                |

|   |      | 7.2.1                   | SSI Interrupt Management Registers              |

|   |      | 7.2.2                   | Mondo Interrupt Vector Register                 |

|   |      | 7.2.3                   | Mondo Data Tables 51                            |

|   |      | 7.2.4                   | Mondo Interrupt Busy Table 52                   |

|   | 7.3  | CPU Inte                | errupt Registers                                |

|   |      | 7.3.1                   | Interrupt Queue Registers 52                    |

|   |      | 7.3.2                   | Interrupt Receive Register                      |

|   |      | 7.3.3                   | Interrupt Vector Dispatch Register              |

|   |      | 7.3.4                   | Incoming Vector Register 56                     |

| 8 |      |                         | els                                             |

|   | 8.1  |                         | ed Memory Models58                              |

|   |      | 8.1.1                   | TSO                                             |

|   |      | 8.1.2                   | RMO 59                                          |

| 9 |      | _                       | es and ASIs                                     |

|   | 9.1  |                         | Address Spaces                                  |

|   |      | 9.1.1                   | Access to Nonexistent Physical Memory Addresses |

|   |      | 9.1.2                   | Access to Nonexistent I/O Addresses 61          |

| 9.1.3         | Instruction Fetching from I/O                                                                                                                                                                                                                                                                                                                                                                          |                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 9.1.4         | Supported vs. Unsupported Access Sizes to I/O                                                                                                                                                                                                                                                                                                                                                          | 62                                                                     |

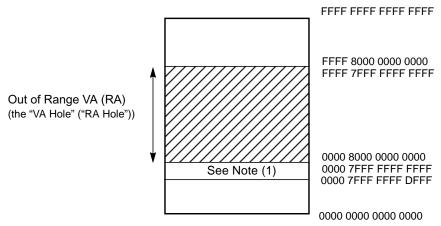

| 9.1.5         | 48-bit Virtual and Real Address Spaces                                                                                                                                                                                                                                                                                                                                                                 | 62                                                                     |

| 9.1.6         | I/O Address Spaces                                                                                                                                                                                                                                                                                                                                                                                     | 64                                                                     |

| 2 Alternate   | Address Spaces                                                                                                                                                                                                                                                                                                                                                                                         | 65                                                                     |

| 9.2.1         | ASI_REAL, ASI_REAL_LITTLE, ASI_REAL_IO, and                                                                                                                                                                                                                                                                                                                                                            |                                                                        |

| 0.2.2         | ASI_REAL_IO_LITTLE /0                                                                                                                                                                                                                                                                                                                                                                                  | 76                                                                     |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               | 8                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                        |

| .2 SPARC Pe   | rformance Instrumentation Counter                                                                                                                                                                                                                                                                                                                                                                      | 84                                                                     |

| .3 DRAM Pe    | rformance Counter                                                                                                                                                                                                                                                                                                                                                                                      | 85                                                                     |

| nplementation | Dependencies                                                                                                                                                                                                                                                                                                                                                                                           | 87                                                                     |

| .1 SPARC V9   | General Information                                                                                                                                                                                                                                                                                                                                                                                    | . 87                                                                   |

| 11.1.1        | Level-2 Compliance (Impdep #1).                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                     |

| 11.1.2        | Unimplemented Opcodes, ASIs, and ILLTRAP                                                                                                                                                                                                                                                                                                                                                               | 87                                                                     |

| 11.1.3        |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

| 11.1.4        | Trap Handling (Impdep #16, 32, 33, 35, 36, 44)                                                                                                                                                                                                                                                                                                                                                         |                                                                        |

| 11.1.5        | SIR Support (Impdep #116)                                                                                                                                                                                                                                                                                                                                                                              | 88                                                                     |

| 11.1.6        | Secure Software                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

| 11.1.7        |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

| 11.1.8        |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

| .2 SPARC V9   | Integer Operations                                                                                                                                                                                                                                                                                                                                                                                     | 89                                                                     |

| 11.2.1        | Integer Register File and Window Control Registers (Impdep #2)                                                                                                                                                                                                                                                                                                                                         |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               | 0 1                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

|               |                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                        |

| 11.4.0        | Supported Memory Models (Inipuep #115, 121)                                                                                                                                                                                                                                                                                                                                                            | ,5                                                                     |

|               | 9.1.4<br>9.1.5<br>9.1.6<br>2 Alternate <i>A</i><br>9.2.1<br>9.2.2<br>9.2.3<br><b>erformance Ins</b><br>1 SPARC Per<br>3 DRAM Per<br><b>plementation</b><br>1 SPARC V9<br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4<br>11.1.5<br>11.1.6<br>11.1.7<br>11.1.8<br>.2 SPARC V9<br>11.2.1<br>11.2.2<br>11.2.3<br>11.2.4<br>11.2.5<br>.3 SPARC V9<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.3.5<br>.4 SPARC V9 | <ul> <li>9.1.4 Supported vs. Unsupported Access Sizes to I/O</li></ul> |

|    |      | 11.4.9    | I/O Operations (Impdep #118, 123) 95                               |

|----|------|-----------|--------------------------------------------------------------------|

|    |      | 11.4.10   | Implicit ASI When TL > 0 (Impdep #124)                             |

|    | 11.5 | Non-SPA   | RC V9 Extensions                                                   |

|    |      | 11.5.1    | Cache Subsystem                                                    |

|    |      | 11.5.2    | Memory Management Unit 95                                          |

|    |      | 11.5.3    | Error Handling                                                     |

|    |      | 11.5.4    | Block Memory Operations 96                                         |

|    |      | 11.5.5    | Partial Stores                                                     |

|    |      | 11.5.6    | Short Floating-Point Loads and Stores                              |

|    |      | 11.5.7    | Load Twin Extended Word 96                                         |

|    |      | 11.5.8    | Interrupt Vector Handling 96                                       |

|    |      | 11.5.9    | Power-Down Support                                                 |

|    |      | 11.5.10   | OpenSPARC T2 Instruction Set Extensions (Impdep #106) 96           |

|    |      | 11.5.11   | Performance Instrumentation                                        |

|    |      | 11.5.12   | Debug and Diagnostics Support                                      |

| 12 | Men  | nory Mana | gement Unit                                                        |

|    | 12.1 |           | on Table Entry (TTE)                                               |

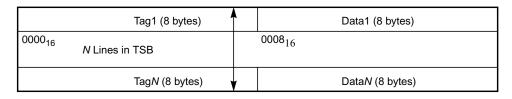

|    | 12.2 |           | on Storage Buffer (TSB)101                                         |

|    | 12.3 |           | e Support for Hypervisor                                           |

|    |      | 12.3.1    | Hardware Support for TSB Access                                    |

|    |      | 12:011    | 12.3.1.1 Hardware Tablewalk                                        |

|    |      |           | 12.3.1.2 Software TLB Reload                                       |

|    |      | 12.3.2    | Real-to-Physical Address Mapping and Speculative Instruction Fetch |

|    |      |           | 109                                                                |

|    | 12.4 | MMU-Re    | lated Faults and Traps                                             |

|    |      | 12.4.1    | fast_instruction_access_MMU_miss Trap                              |

|    |      | 12.4.2    | instruction_access_MMU_miss Trap.                                  |

|    |      | 12.4.3    | instruction_real_translation_miss Trap 112                         |

|    |      | 12.4.4    | instruction_invalid_TSB_entry Trap 112                             |

|    |      | 12.4.5    | IAE_privilege_violation Trap 112                                   |

|    |      | 12.4.6    | IAE_unauth_access Trap 112                                         |

|    |      | 12.4.7    | IAE_nfo_page Trap 113                                              |

|    |      | 12.4.8    | instruction_address_range Trap 113                                 |

|    |      | 12.4.9    | instruction_real_range Trap 113                                    |

|    |      | 12.4.10   | fast_data_access_MMU_miss Trap 113                                 |

|    |      | 12.4.11   | data_access_MMU_miss Trap 113                                      |

|    |      | 12.4.12   | data_invalid_TSB_entry Trap 114                                    |

|    |      | 12.4.13   | data_real_translation_miss Trap                                    |

|    |      | 12.4.14   | DAE_privilege_violation Trap                                       |

|    |      | 12.4.15   | DAE_side_effect_page Trap                                          |

|    |      | 12.4.16   | DAE_nc_page Trap                                                   |

|    |      | 12.4.17   | DAE_invalid_asi Trap                                               |

|    |      | 12.4.18   | DAE_nfo_page Trap                                                  |

|    |      | 12.4.19   | mem_address_range Trap                                             |

|    |      | 12.4.20   | <i>mem_real_range</i> Trap 115                                     |

|    | 12.4.21            | fast_data_access_protection Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 115 |

|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 12.4.22            | privileged_action Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 116 |

|    | 12.4.23            | instruction_VA_watchpoint Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 116 |

|    | 12.4.24            | VA_watchpoint Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 116 |

|    | 12.4.25            | PA_watchpoint Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 116 |

|    | 12.4.26            | *_mem_address_not_aligned Traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|    | 12.4.27            | Unsupported_page_size Trap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|    | 12.5 MMU O         | peration Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|    |                    | e, Context, and Endianness Selection for Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|    |                    | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|    | 12.7.1             | Instruction Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|    | 12.7.1             | 12.7.1.1 Instruction Prefetching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|    | 12.7.2             | Data Translation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|    |                    | Phavior During Reset and Upon Entering RED_state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|    |                    | nce With the SPARC V9 Annex F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|    | -                  | ternal Registers and ASI Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|    | 12.10.1            | Accessing MMU Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|    | 12.10.2            | Context Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|    | 12.10.3            | I-/D-TSB Tag Target Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|    | 12.10.4            | I-/D-MMU Synchronous Fault Address Registers (SFAR).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|    |                    | 12.10.4.1 I-MMU Fault Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|    | 10 10 F            | 12.10.4.2 D-MMU Fault Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|    | 12.10.5            | I-/D-TLB Tag Access Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |